Edge-triggered hardware circuits respond to changes in input signals at specific transitions, such as the rising or falling edges of a clock pulse, enabling precise timing control in synchronous systems. Level-triggered circuits activate based on the continuous presence of a particular signal level, making them more sensitive to input duration rather than instantaneous transitions. Choosing between edge-triggered and level-triggered designs depends on factors like timing accuracy, complexity, and power consumption in hardware engineering applications.

Table of Comparison

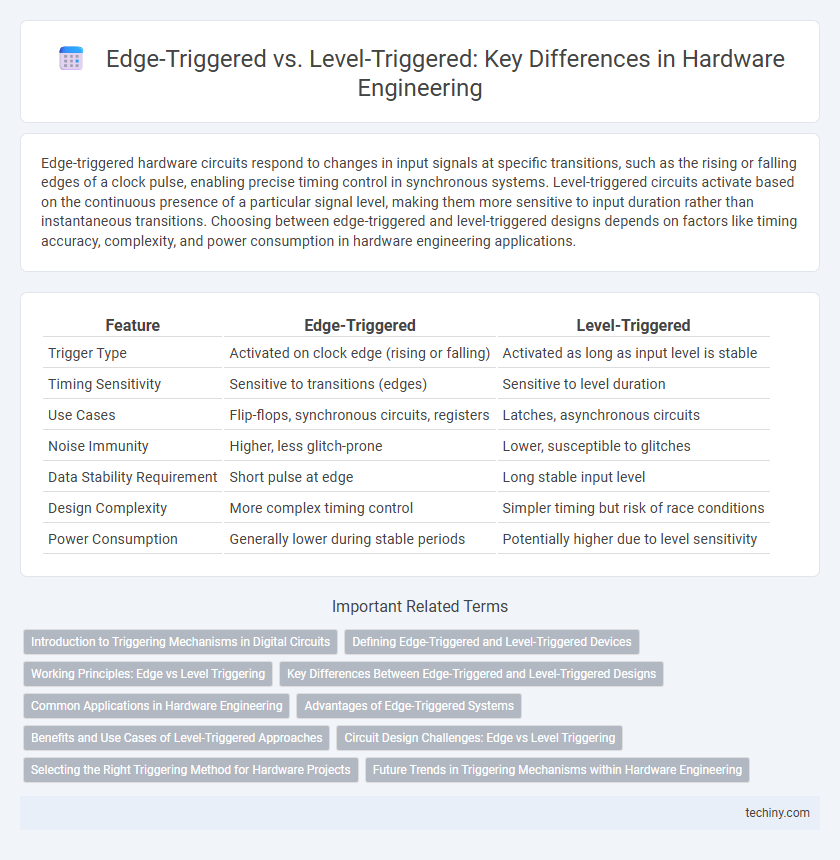

| Feature | Edge-Triggered | Level-Triggered |

|---|---|---|

| Trigger Type | Activated on clock edge (rising or falling) | Activated as long as input level is stable |

| Timing Sensitivity | Sensitive to transitions (edges) | Sensitive to level duration |

| Use Cases | Flip-flops, synchronous circuits, registers | Latches, asynchronous circuits |

| Noise Immunity | Higher, less glitch-prone | Lower, susceptible to glitches |

| Data Stability Requirement | Short pulse at edge | Long stable input level |

| Design Complexity | More complex timing control | Simpler timing but risk of race conditions |

| Power Consumption | Generally lower during stable periods | Potentially higher due to level sensitivity |

Introduction to Triggering Mechanisms in Digital Circuits

Edge-triggered mechanisms activate a flip-flop or latch only at the transition edge (rising or falling) of a clock signal, ensuring precise timing control in sequential circuits. Level-triggered mechanisms respond to the clock signal's level (high or low) over a duration, allowing data to flow as long as the clock is at a specific state, which can cause glitches or unintended behavior. Edge-triggered triggering is preferred in high-speed digital systems for its resistance to timing hazards, while level-triggered is simpler but less reliable under complex timing conditions.

Defining Edge-Triggered and Level-Triggered Devices

Edge-triggered devices respond to changes in input signals only at specific transitions, such as rising or falling edges, enabling precise timing control in hardware circuits. Level-triggered devices activate when the input signal reaches a certain level, maintaining the output state as long as the input remains at that level. This fundamental distinction impacts the design of flip-flops, latches, and synchronization mechanisms in digital systems.

Working Principles: Edge vs Level Triggering

Edge-triggered devices respond to specific transitions in the clock signal, such as the rising or falling edge, ensuring data capture only at those precise moments. Level-triggered devices remain sensitive as long as the clock signal maintains a particular level, continuously allowing data flow during the active phase. This fundamental difference impacts timing accuracy and synchronization in digital circuit design, with edge-triggered systems reducing data ambiguity and level-triggered systems offering simpler control schemes.

Key Differences Between Edge-Triggered and Level-Triggered Designs

Edge-triggered designs respond exclusively to signal transitions, capturing data on rising or falling clock edges, which enhances timing accuracy and reduces glitches in synchronous circuits. Level-triggered designs are sensitive throughout the duration of an active signal level, enabling continuous data flow but increasing vulnerability to noise and timing errors. The choice between edge-triggered and level-triggered architectures significantly impacts circuit complexity, synchronization reliability, and overall system performance in hardware engineering.

Common Applications in Hardware Engineering

Edge-triggered devices are widely used in synchronous circuits such as flip-flops and registers, enabling precise timing control by responding to signal transitions. Level-triggered components find common applications in latches and memory devices, where maintaining a stable output during a signal level is critical. Both trigger types play essential roles in designing finite state machines and clocked sequential logic, optimizing performance and reliability in digital hardware systems.

Advantages of Edge-Triggered Systems

Edge-triggered systems offer precise timing control by responding exclusively to signal transitions, reducing the risk of metastability and timing errors in digital circuits. These systems enable higher clock speeds and improved synchronization in complex hardware designs, enhancing overall system reliability. Edge-triggered mechanisms also minimize power consumption by activating only during state changes, making them ideal for high-performance, energy-efficient hardware engineering applications.

Benefits and Use Cases of Level-Triggered Approaches

Level-triggered circuits offer increased stability and noise immunity by responding continuously to input signals while they maintain a specific logic level, making them ideal for applications requiring reliable signal detection. They simplify timing analysis in hardware designs by eliminating the need to precisely track signal transitions, which benefits systems with slow or asynchronous inputs. Common use cases include memory latching, input debouncing, and control signal monitoring where persistent state observation is critical.

Circuit Design Challenges: Edge vs Level Triggering

Edge-triggered circuits face challenges with precise timing requirements and susceptibility to clock skew, demanding careful synchronization to avoid metastability in flip-flops. Level-triggered designs simplify timing by maintaining a signal state throughout the clock pulse but raise issues with pulse width and hold time violations, complicating latch transparency control. Balancing these constraints influences circuit reliability, latency, and power consumption in hardware engineering.

Selecting the Right Triggering Method for Hardware Projects

Edge-triggered circuits respond only at the moment of signal transition, offering precise timing control essential for synchronous systems in hardware projects. Level-triggered circuits remain active while the input signal is at a specific logic level, providing simpler design but potential risks of signal glitches in complex timing scenarios. Selecting the right triggering method depends on application requirements such as timing accuracy, noise tolerance, and system complexity in hardware engineering.

Future Trends in Triggering Mechanisms within Hardware Engineering

Future trends in triggering mechanisms within hardware engineering emphasize the integration of adaptive edge-triggered circuits that enhance timing accuracy and power efficiency in increasingly complex systems. Innovations in level-triggered designs are geared towards hybrid models combining both edge and level sensitivity to optimize signal integrity and noise immunity in high-speed applications. Emerging technologies also focus on leveraging machine learning algorithms to dynamically adjust triggering thresholds, improving reliability and performance in heterogeneous computing environments.

Edge-triggered vs Level-triggered Infographic

techiny.com

techiny.com