Static Timing Analysis (STA) evaluates the timing performance of a digital circuit without requiring input vectors, ensuring all possible paths meet timing constraints through mathematical modeling. Dynamic Timing Analysis, on the other hand, simulates circuit behavior using specific input patterns to observe timing under realistic operational conditions. While STA provides exhaustive coverage for worst-case scenarios, Dynamic Analysis captures real-time effects like glitches and data-dependent delays.

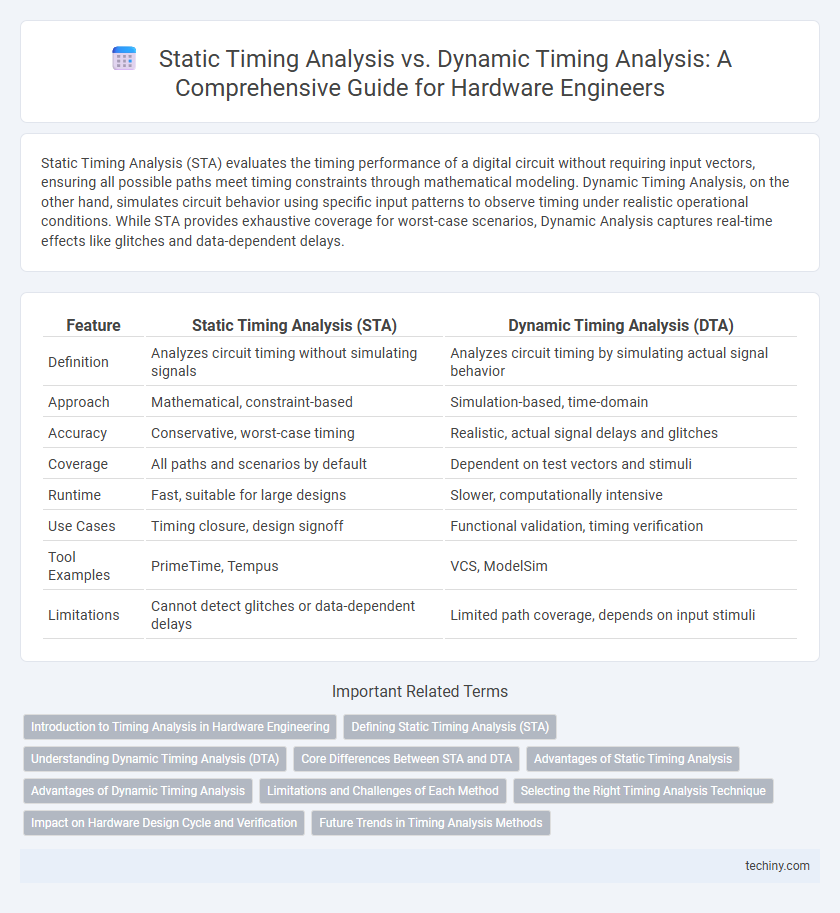

Table of Comparison

| Feature | Static Timing Analysis (STA) | Dynamic Timing Analysis (DTA) |

|---|---|---|

| Definition | Analyzes circuit timing without simulating signals | Analyzes circuit timing by simulating actual signal behavior |

| Approach | Mathematical, constraint-based | Simulation-based, time-domain |

| Accuracy | Conservative, worst-case timing | Realistic, actual signal delays and glitches |

| Coverage | All paths and scenarios by default | Dependent on test vectors and stimuli |

| Runtime | Fast, suitable for large designs | Slower, computationally intensive |

| Use Cases | Timing closure, design signoff | Functional validation, timing verification |

| Tool Examples | PrimeTime, Tempus | VCS, ModelSim |

| Limitations | Cannot detect glitches or data-dependent delays | Limited path coverage, depends on input stimuli |

Introduction to Timing Analysis in Hardware Engineering

Static Timing Analysis (STA) evaluates the worst-case timing behavior of digital circuits by analyzing all possible signal paths without requiring input vectors or simulation, ensuring comprehensive timing verification. Dynamic Timing Analysis relies on simulation with specific input vectors to observe circuit behavior under realistic operating conditions, capturing data-dependent timing variations. Both methods are essential for verifying timing constraints in hardware engineering, with STA providing exhaustive path coverage and Dynamic Timing Analysis offering detailed performance insights.

Defining Static Timing Analysis (STA)

Static Timing Analysis (STA) is a method used in hardware engineering to evaluate the timing performance of digital circuits without requiring input vectors or simulation vectors, providing a comprehensive timing check across all possible operational scenarios. STA calculates the worst-case delay through paths in a circuit by analyzing timing constraints such as setup time, hold time, and clock skew to ensure reliable operation at target clock speeds. This technique is critical for verifying timing closure in complex integrated circuits, reducing the risk of timing violations and improving design robustness.

Understanding Dynamic Timing Analysis (DTA)

Dynamic Timing Analysis (DTA) evaluates the actual signal propagation delays through a hardware circuit during operation by simulating real input patterns and capturing glitch behaviors, providing a more accurate timing characterization than Static Timing Analysis (STA). It models circuit activity under various switching conditions, capturing data-dependent variations and transient faults that STA might overlook. DTA is essential for verifying timing under realistic workloads, identifying critical path delays missed in worst-case scenarios and improving design reliability in complex hardware systems.

Core Differences Between STA and DTA

Static Timing Analysis (STA) evaluates all possible signal paths in a digital circuit without requiring simulation vectors, providing worst-case timing estimates based on fixed timing models. Dynamic Timing Analysis (DTA) relies on simulation with specific input vectors to analyze actual signal transitions and glitch occurrences, capturing real-time behavior and environmental effects. STA offers comprehensive coverage and faster verification, whereas DTA provides detailed insights into dynamic phenomena and is more computationally intensive.

Advantages of Static Timing Analysis

Static Timing Analysis offers comprehensive verification of all possible signal paths without requiring circuit simulation, ensuring early detection of timing violations. It provides faster analysis times and scalability for complex designs compared to Dynamic Timing Analysis, enabling efficient optimization during hardware development. This method is less resource-intensive and guarantees timing closure across all operating conditions and corner cases, improving overall design reliability.

Advantages of Dynamic Timing Analysis

Dynamic Timing Analysis offers the advantage of more accurate timing verification by simulating real operating conditions, capturing data-dependent and environmental variations that static timing analysis might overlook. It enables detection of rare timing violations caused by specific input transitions and path correlations, providing higher confidence in circuit reliability. This method also facilitates early identification of potential timing failures under realistic workloads, improving overall hardware performance and robustness.

Limitations and Challenges of Each Method

Static Timing Analysis (STA) faces limitations in accurately modeling complex path behavior, process variations, and real-world operational conditions, often leading to pessimistic timing estimates. Dynamic Timing Analysis (DTA) challenges include high computational overhead, dependency on detailed waveform data, and limited scalability for large, complex designs. Both methods struggle with accurately accounting for signal integrity issues and environmental variations, necessitating hybrid approaches for comprehensive timing validation.

Selecting the Right Timing Analysis Technique

Selecting the right timing analysis technique in hardware engineering depends on the specific design requirements and constraints. Static Timing Analysis (STA) offers comprehensive coverage of all possible paths, ensuring worst-case timing validation without requiring test vectors, while Dynamic Timing Analysis (DTA) provides timing validation under actual input conditions, capturing data-dependent behavior and glitches. Engineers prioritize STA for broad timing verification in complex integrated circuits, whereas DTA is preferred when accurate modeling of functional behavior and signal transitions is critical.

Impact on Hardware Design Cycle and Verification

Static Timing Analysis (STA) accelerates the hardware design cycle by providing fast, comprehensive timing verification without requiring simulation stimuli, enabling early detection of timing violations. Dynamic Timing Analysis (DTA) offers detailed verification under specific workloads but demands extensive simulation time, slowing iteration during hardware design. Integrating STA ensures efficient timing closure, while selective DTA enhances confidence in design reliability through workload-specific validation.

Future Trends in Timing Analysis Methods

Future trends in timing analysis methods emphasize the integration of machine learning algorithms to enhance the accuracy and efficiency of both static and dynamic timing analysis. Advanced AI-driven predictive models analyze complex timing behaviors under various process variations and environmental conditions, enabling real-time adaptive optimization in hardware design. The evolution of multi-physics simulation tools combined with timing analysis frameworks is expected to improve the reliability and robustness of next-generation integrated circuits.

Static Timing Analysis vs Dynamic Timing Analysis Infographic

techiny.com

techiny.com