Quantum circuit depth and circuit width are critical metrics that influence the performance and scalability of quantum algorithms. Circuit depth refers to the number of sequential quantum gates applied, directly impacting coherence time and error rates, while circuit width indicates the number of qubits involved, affecting parallelism and resource requirements. Balancing circuit depth and width is essential for optimizing quantum computations, as reducing depth can mitigate decoherence but often increases width, necessitating efficient designs that minimize both parameters for practical quantum advantage.

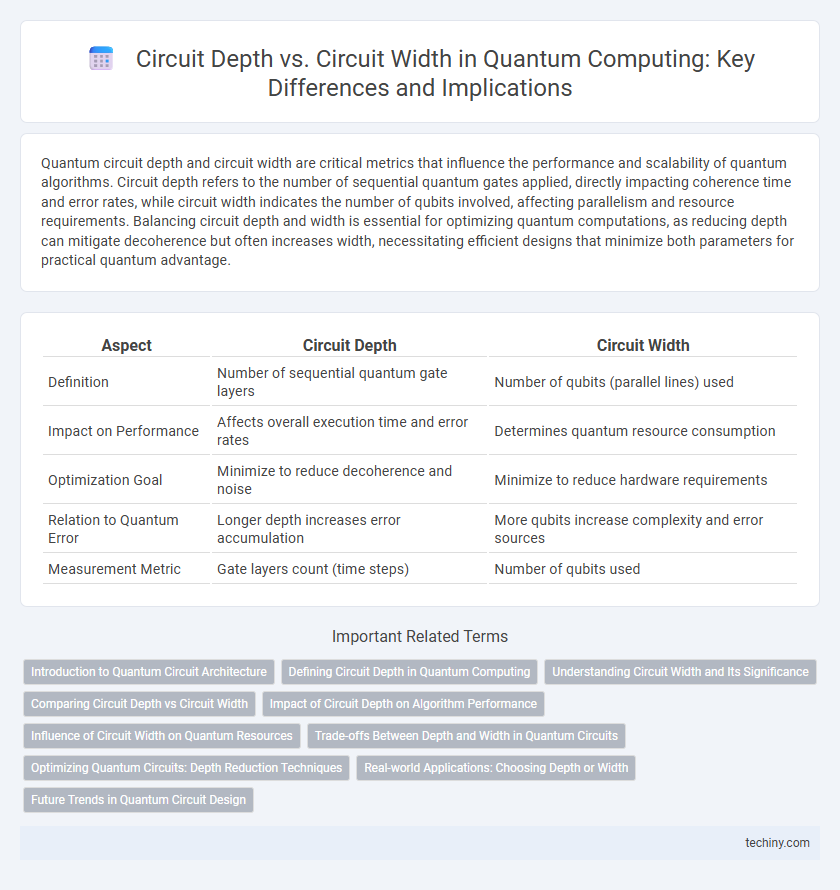

Table of Comparison

| Aspect | Circuit Depth | Circuit Width |

|---|---|---|

| Definition | Number of sequential quantum gate layers | Number of qubits (parallel lines) used |

| Impact on Performance | Affects overall execution time and error rates | Determines quantum resource consumption |

| Optimization Goal | Minimize to reduce decoherence and noise | Minimize to reduce hardware requirements |

| Relation to Quantum Error | Longer depth increases error accumulation | More qubits increase complexity and error sources |

| Measurement Metric | Gate layers count (time steps) | Number of qubits used |

Introduction to Quantum Circuit Architecture

Quantum circuit architecture is fundamentally characterized by circuit depth and circuit width, where depth refers to the number of sequential quantum gate layers and width denotes the total number of qubits involved. Minimizing circuit depth is critical to reduce quantum decoherence effects, while circuit width directly impacts the hardware resource requirements and scalability of quantum algorithms. Optimizing the trade-off between depth and width is essential for enhancing quantum computational efficiency and stability in practical implementations.

Defining Circuit Depth in Quantum Computing

Circuit depth in quantum computing refers to the total number of sequential quantum gate layers applied during a quantum algorithm, measuring the time complexity of quantum circuits. It directly impacts decoherence and error rates, making shallower circuits essential for near-term quantum devices with limited coherence times. Minimizing circuit depth while balancing circuit width, defined as the number of qubits, is critical for optimizing quantum algorithm performance and hardware efficiency.

Understanding Circuit Width and Its Significance

Circuit width in quantum computing refers to the number of qubits employed simultaneously during computation, directly influencing the complexity and scalability of quantum algorithms. A wider circuit allows parallel processing of more quantum bits, enhancing computational power but increasing error susceptibility and resource demands. Managing circuit width effectively is crucial for optimizing quantum hardware performance and achieving fault-tolerant quantum operations.

Comparing Circuit Depth vs Circuit Width

Circuit depth measures the number of sequential quantum gate layers applied, influencing total computation time and error accumulation in a quantum algorithm. Circuit width refers to the number of qubits operated on simultaneously, directly affecting hardware resource requirements and parallelism potential. Optimal quantum circuit design balances minimal depth to reduce decoherence effects against manageable width to fit within available quantum hardware constraints.

Impact of Circuit Depth on Algorithm Performance

Circuit depth in quantum computing directly affects algorithm performance by increasing the likelihood of decoherence and quantum noise, thereby reducing the fidelity of computational results. Shallow circuits with minimal depth enable faster execution and lower error rates, which is critical for near-term quantum hardware limited by coherence time. Optimizing circuit depth minimizes gate operations, enhancing algorithm accuracy and enabling more reliable quantum advantage in practical applications.

Influence of Circuit Width on Quantum Resources

Circuit width, defined by the number of qubits used in a quantum algorithm, significantly impacts quantum resource requirements such as coherence time and error rates. Increasing circuit width demands more qubits, which elevates the need for error correction and qubit connectivity, influencing overall hardware scalability. Optimizing circuit width helps balance resource constraints and algorithmic performance, enabling more efficient quantum computations.

Trade-offs Between Depth and Width in Quantum Circuits

Trade-offs between circuit depth and width are crucial in quantum circuits as increasing the depth often improves computational power but raises error rates due to decoherence, while expanding width demands more qubits, which remain a scarce resource. Optimizing these parameters involves balancing gate fidelity, coherence times, and qubit connectivity to minimize error accumulation and resource overhead. Techniques like circuit compression reduce depth at the cost of wider circuits, whereas parallel execution cuts width requirements but can increase overall depth.

Optimizing Quantum Circuits: Depth Reduction Techniques

Optimizing quantum circuits involves reducing circuit depth to minimize decoherence and error rates, which is crucial for practical quantum computation. Techniques such as gate commutation, parallel execution of operations, and exploiting native multi-qubit gates effectively lower circuit depth without significantly increasing circuit width. Leveraging these depth reduction strategies enables more efficient quantum algorithms and improves overall quantum processor performance by balancing trade-offs between coherence time and qubit resource utilization.

Real-world Applications: Choosing Depth or Width

Real-world quantum computing applications demand a strategic balance between circuit depth and circuit width to optimize performance and resource utilization. Circuit depth impacts coherence time and error rates, making shallower circuits essential for near-term noisy intermediate-scale quantum (NISQ) devices, while wider circuits enable greater parallelism and qubit connectivity in applications like quantum chemistry simulations and optimization problems. Practical implementations often prioritize circuit width to exploit available qubit counts but simultaneously minimize depth to reduce noise accumulation and maximize fidelity in quantum machine learning and cryptographic algorithms.

Future Trends in Quantum Circuit Design

Future trends in quantum circuit design emphasize balancing circuit depth and width to optimize quantum error rates and coherence times. Reducing circuit depth minimizes decoherence, while increasing circuit width enables parallelism and scalability in qubit operations. Innovations in hardware architecture and error-correcting codes aim to achieve fault-tolerant quantum computation with efficient depth-width trade-offs.

circuit depth vs circuit width Infographic

techiny.com

techiny.com