Bus arbitration coordinates access to a shared communication bus by controlling which device can initiate data transfers at a given time, ensuring orderly and conflict-free communication. In contrast, bus mastering allows a device to take control of the bus and manage data transfers independently, improving efficiency by reducing CPU intervention. Understanding the differences between bus arbitration and bus mastering is crucial for designing optimized hardware systems with seamless data flow and resource sharing.

Table of Comparison

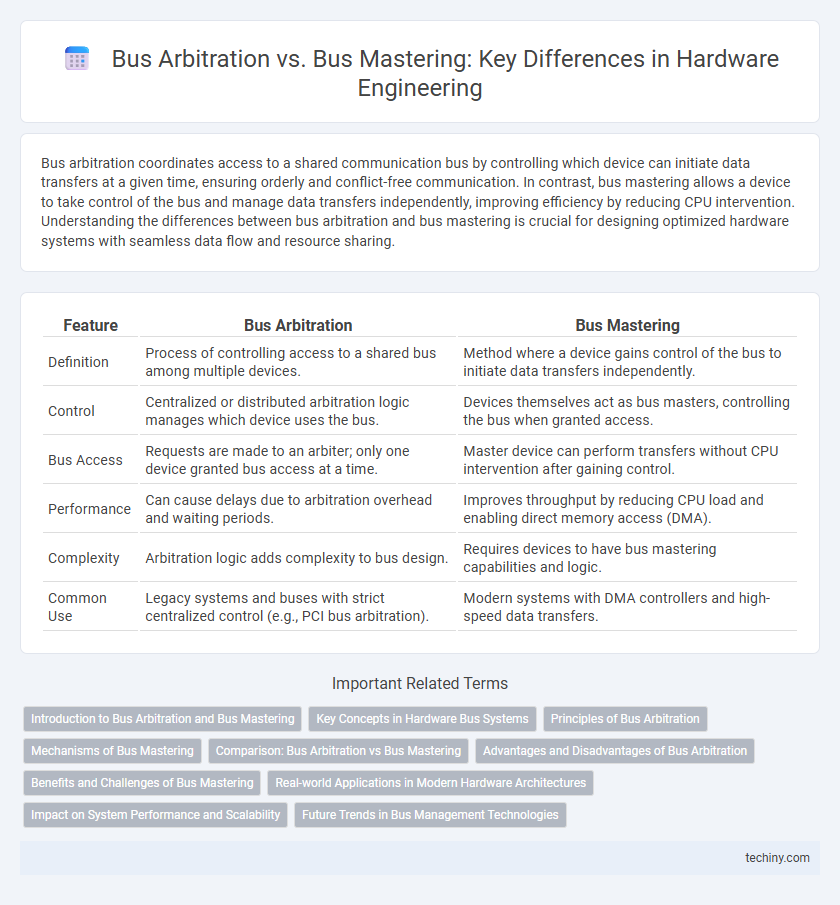

| Feature | Bus Arbitration | Bus Mastering |

|---|---|---|

| Definition | Process of controlling access to a shared bus among multiple devices. | Method where a device gains control of the bus to initiate data transfers independently. |

| Control | Centralized or distributed arbitration logic manages which device uses the bus. | Devices themselves act as bus masters, controlling the bus when granted access. |

| Bus Access | Requests are made to an arbiter; only one device granted bus access at a time. | Master device can perform transfers without CPU intervention after gaining control. |

| Performance | Can cause delays due to arbitration overhead and waiting periods. | Improves throughput by reducing CPU load and enabling direct memory access (DMA). |

| Complexity | Arbitration logic adds complexity to bus design. | Requires devices to have bus mastering capabilities and logic. |

| Common Use | Legacy systems and buses with strict centralized control (e.g., PCI bus arbitration). | Modern systems with DMA controllers and high-speed data transfers. |

Introduction to Bus Arbitration and Bus Mastering

Bus arbitration is a hardware mechanism that controls access to a shared communication bus by managing multiple device requests, ensuring orderly and conflict-free data transmission. Bus mastering allows a device to take control of the bus to initiate direct data transfers without CPU intervention, enhancing system efficiency during high data throughput operations. Efficient bus arbitration protocols and bus mastering capabilities play a crucial role in optimizing performance and resource allocation in complex hardware systems.

Key Concepts in Hardware Bus Systems

Bus arbitration determines which device gains control of the bus at any given time through a centralized or distributed control mechanism, ensuring orderly access and preventing data collisions. Bus mastering allows a device to take control of the bus and directly communicate with memory or peripherals without CPU intervention, improving data transfer efficiency. Key concepts include arbitration protocols like centralized, distributed, or daisy chain, and bus mastering techniques which impact bus latency and throughput in hardware systems.

Principles of Bus Arbitration

Bus arbitration governs access control to a shared communication bus in hardware engineering, ensuring that multiple devices do not transmit simultaneously, which could cause data collisions. This process involves a centralized or distributed arbitration scheme where requests from devices are prioritized and granted bus access based on fairness or predetermined priority levels. Effective bus arbitration maintains system stability and maximizes data transfer efficiency by coordinating device communication timing on the bus.

Mechanisms of Bus Mastering

Bus mastering enables multiple devices to take control of the data bus, allowing them to initiate and manage data transfers independently without CPU intervention. This mechanism uses arbitration circuits to resolve conflicts when several devices request bus access simultaneously, ensuring orderly communication. Hardware components such as priority encoders and grant signals play crucial roles in dynamically selecting the bus master based on predefined priority levels.

Comparison: Bus Arbitration vs Bus Mastering

Bus arbitration and bus mastering are critical techniques in hardware engineering for managing control of the system bus. Bus arbitration involves a central controller allocating bus access to multiple devices based on priority or fairness algorithms, ensuring orderly communication but potentially introducing latency. Bus mastering allows devices to take control of the bus independently to initiate data transfers, improving efficiency and throughput by reducing bottlenecks associated with centralized arbitration.

Advantages and Disadvantages of Bus Arbitration

Bus arbitration ensures orderly control of the data bus by assigning priority to multiple bus requesters, preventing data collisions and improving system stability. Its advantages include simplified hardware design and predictable access times, but disadvantages involve potential delays due to arbitration overhead and limited efficiency under high bus contention. Bus arbitration can become a bottleneck in high-performance systems compared to bus mastering, where devices directly control the bus for faster data transfer.

Benefits and Challenges of Bus Mastering

Bus mastering allows multiple devices to control the bus independently, improving data throughput and reducing CPU overhead by enabling peripherals to communicate directly with memory. The benefits include increased system efficiency and faster data transfer rates, particularly in complex hardware environments. Challenges involve managing bus contention and ensuring synchronized access, which requires sophisticated arbitration protocols and can increase design complexity.

Real-world Applications in Modern Hardware Architectures

Bus arbitration ensures controlled access to the communication bus by multiple devices, preventing conflicts during data transmission in complex hardware systems. Bus mastering allows peripherals to directly control the bus and communicate with memory or other devices without CPU intervention, increasing data throughput and reducing latency. Modern hardware architectures leverage bus mastering in high-speed interfaces like PCI Express, while bus arbitration remains critical in shared-bus environments such as legacy PCI and embedded systems.

Impact on System Performance and Scalability

Bus arbitration controls access to the shared communication bus by granting permission to one device at a time, which can introduce latency and limit system throughput in hardware engineering. Bus mastering enables devices to take control of the bus independently, enhancing system performance by allowing parallel data transfers and reducing CPU bottlenecks. Scalability improves with bus mastering as systems can support multiple high-speed devices concurrently, whereas bus arbitration systems may face contention and delay as device count increases.

Future Trends in Bus Management Technologies

Emerging trends in bus management technologies emphasize enhanced bus arbitration algorithms that leverage machine learning to optimize resource allocation and reduce latency in complex hardware systems. Innovations in bus mastering are integrating adaptive control mechanisms that enable more autonomous and efficient data transfer between peripherals, minimizing CPU involvement and boosting overall system performance. Future bus management solutions will likely combine dynamic arbitration with intelligent bus mastering to support the increasing demand for high-speed, low-power communication in advanced hardware architectures.

Bus arbitration vs Bus mastering Infographic

techiny.com

techiny.com