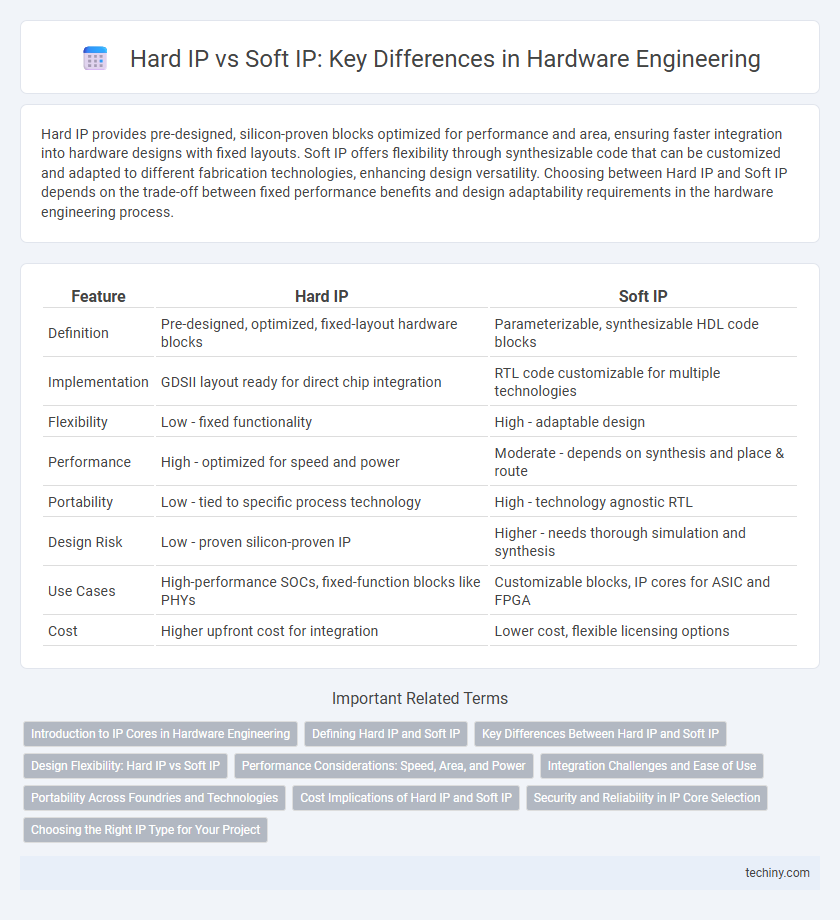

Hard IP provides pre-designed, silicon-proven blocks optimized for performance and area, ensuring faster integration into hardware designs with fixed layouts. Soft IP offers flexibility through synthesizable code that can be customized and adapted to different fabrication technologies, enhancing design versatility. Choosing between Hard IP and Soft IP depends on the trade-off between fixed performance benefits and design adaptability requirements in the hardware engineering process.

Table of Comparison

| Feature | Hard IP | Soft IP |

|---|---|---|

| Definition | Pre-designed, optimized, fixed-layout hardware blocks | Parameterizable, synthesizable HDL code blocks |

| Implementation | GDSII layout ready for direct chip integration | RTL code customizable for multiple technologies |

| Flexibility | Low - fixed functionality | High - adaptable design |

| Performance | High - optimized for speed and power | Moderate - depends on synthesis and place & route |

| Portability | Low - tied to specific process technology | High - technology agnostic RTL |

| Design Risk | Low - proven silicon-proven IP | Higher - needs thorough simulation and synthesis |

| Use Cases | High-performance SOCs, fixed-function blocks like PHYs | Customizable blocks, IP cores for ASIC and FPGA |

| Cost | Higher upfront cost for integration | Lower cost, flexible licensing options |

Introduction to IP Cores in Hardware Engineering

IP cores in hardware engineering are pre-designed functional blocks used to accelerate system design and reduce development time. Hard IP cores are physically implemented and optimized for performance and area, offering predictable timing and power characteristics, while soft IP cores provide synthesizable RTL code, enabling greater flexibility and portability across different manufacturing processes. Designers choose between hard and soft IP based on project requirements, balancing customization needs with performance constraints.

Defining Hard IP and Soft IP

Hard IP refers to pre-designed, fixed-function hardware blocks with physical layout and timing information optimized for specific semiconductor processes, enabling faster integration and predictable performance. Soft IP consists of synthesizable hardware description language (HDL) code, offering flexibility for customization and adaptation across different manufacturing technologies and design requirements. Both types of IP cores play crucial roles in modern system-on-chip (SoC) design by balancing the trade-offs between performance, flexibility, and reusability.

Key Differences Between Hard IP and Soft IP

Hard IP refers to pre-designed, fixed-function hardware blocks with optimized layouts and verified timing, offering faster integration and predictable performance in ASIC or FPGA designs. Soft IP consists of synthesizable RTL code, providing greater flexibility and portability across different process technologies but requiring additional synthesis, placement, and routing steps. The key differences lie in their implementation form, customization level, and impact on design cycle time and performance predictability.

Design Flexibility: Hard IP vs Soft IP

Hard IP offers limited design flexibility due to its fixed layout and predefined parameters, making it ideal for high-performance, area-critical applications. Soft IP provides extensive design flexibility with synthesizable RTL code, allowing customization and adaptation to different process technologies and design requirements. Engineers often prefer Soft IP for rapid prototyping and design iteration, while Hard IP is favored for stable, optimized hardwired functions.

Performance Considerations: Speed, Area, and Power

Hard IP cores offer optimized speed, reduced area, and lower power consumption due to their fixed, pre-verified physical layout tailored for specific processes. Soft IP cores provide design flexibility but may require additional optimization efforts, often resulting in increased area and power overheads while potentially limiting achievable speed. Performance trade-offs between Hard IP and Soft IP are critical in hardware engineering decisions, depending on the target application's requirements for speed, footprint, and energy efficiency.

Integration Challenges and Ease of Use

Hard IP offers fixed, pre-verified physical layouts that simplify timing closure and reduce integration risks but limit customization and require careful matching with the target process technology. Soft IP, provided as synthesizable RTL, allows greater flexibility and easier adaptation to different fabrication processes but demands more design effort to ensure performance and area optimization. Integration challenges with Hard IP mainly involve process compatibility, while Soft IP requires thorough verification and optimization during implementation.

Portability Across Foundries and Technologies

Hard IP cores offer limited portability as they are optimized for specific foundries and process nodes, leading to challenges in adapting to different manufacturing technologies. Soft IP cores, designed in synthesizable RTL code, provide greater flexibility and can be mapped to various foundries and technology nodes with minimal modification. This adaptability makes Soft IP more suitable for designs requiring frequent technology migration or multiple foundry support.

Cost Implications of Hard IP and Soft IP

Hard IP typically involves higher upfront costs due to licensing fees and integration complexity but offers lower long-term expenses through optimized performance and reduced rework. Soft IP, being more flexible and source-code based, generally incurs lower initial costs but can lead to increased verification, customization, and potential redesign expenses. Evaluating cost implications depends on project scale, time-to-market requirements, and resource availability in hardware engineering.

Security and Reliability in IP Core Selection

Hard IP cores offer enhanced security through fixed, pre-verified designs that reduce the attack surface and prevent unauthorized modifications, making them ideal for secure hardware applications. Soft IP cores provide flexibility and adaptability but require rigorous verification to ensure reliability and may introduce vulnerabilities if not carefully managed. Selecting IP cores involves balancing the immutable security benefits of Hard IP with the customizable advantages of Soft IP to meet specific system reliability and protection requirements.

Choosing the Right IP Type for Your Project

Choosing between Hard IP and Soft IP in hardware engineering depends on project requirements such as performance, flexibility, and integration complexity. Hard IPs provide optimized, pre-verified blocks that ensure high performance and reduced risk but lack adaptability, making them ideal for applications with stringent timing and area constraints. Soft IPs offer RTL-level flexibility that enables customization and easier technology migration, suitable for designs demanding rapid innovation and scalability.

Hard IP vs Soft IP Infographic

techiny.com

techiny.com