Parity bit provides a simple method for detecting single-bit errors in data transmission by adding an extra bit to indicate whether the number of ones is even or odd. ECC (Error Correcting Code) goes beyond detection by identifying and correcting multiple-bit errors, enhancing data integrity in memory and storage systems. While parity bits are useful for basic error detection with minimal overhead, ECC is essential in critical applications requiring robust error correction and reliability.

Table of Comparison

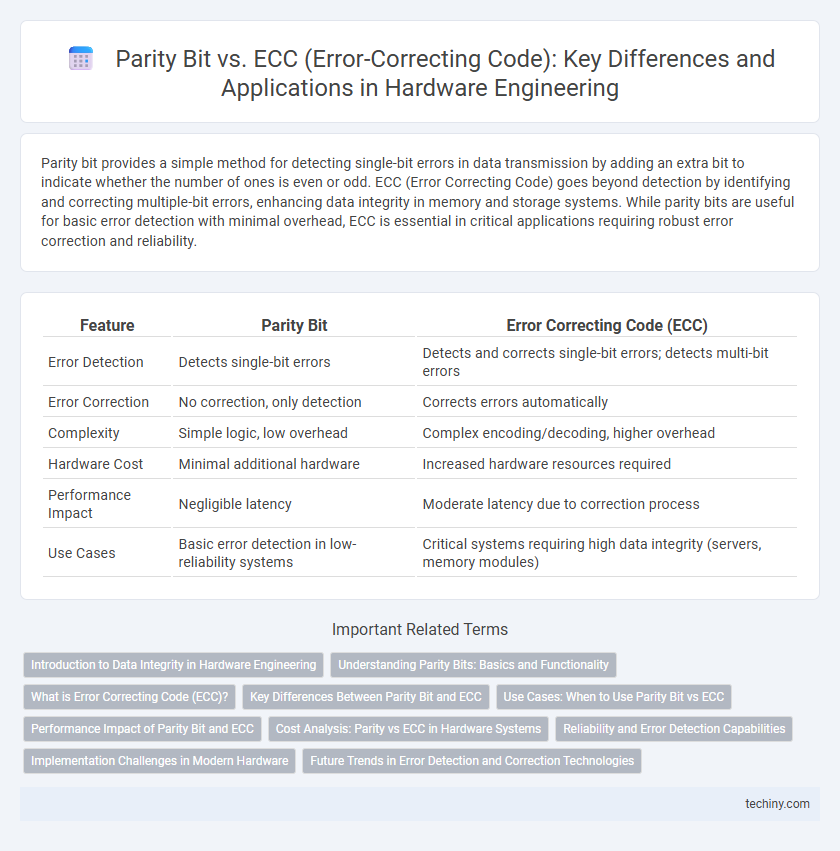

| Feature | Parity Bit | Error Correcting Code (ECC) |

|---|---|---|

| Error Detection | Detects single-bit errors | Detects and corrects single-bit errors; detects multi-bit errors |

| Error Correction | No correction, only detection | Corrects errors automatically |

| Complexity | Simple logic, low overhead | Complex encoding/decoding, higher overhead |

| Hardware Cost | Minimal additional hardware | Increased hardware resources required |

| Performance Impact | Negligible latency | Moderate latency due to correction process |

| Use Cases | Basic error detection in low-reliability systems | Critical systems requiring high data integrity (servers, memory modules) |

Introduction to Data Integrity in Hardware Engineering

Parity bit provides a simple error detection method by adding a single bit to data, checking whether the number of set bits is odd or even, thus identifying single-bit errors. ECC (Error Correcting Code) offers a more advanced approach, detecting and correcting multiple-bit errors to enhance data integrity in critical hardware systems. Both techniques are fundamental in hardware engineering to ensure reliable data transmission and storage, minimizing corruption risks in memory modules and communication channels.

Understanding Parity Bits: Basics and Functionality

Parity bits are a simple error detection mechanism used in hardware engineering to identify single-bit errors in data transmission or storage by adding an extra bit that indicates whether the number of 1s in a data set is odd or even. Unlike ECC (Error Correcting Code), which can detect and correct multiple-bit errors, parity bits only provide error detection without correction capabilities, making them less complex but also less reliable for critical applications. Understanding the functionality of parity bits is essential for designing systems that require basic integrity checks with minimal overhead, especially in memory modules and communication interfaces.

What is Error Correcting Code (ECC)?

Error Correcting Code (ECC) is a method used in hardware engineering to detect and correct data corruption in memory storage systems. ECC works by adding redundant bits to data, enabling the identification and automatic correction of single-bit errors and detection of multi-bit errors, thereby improving system reliability. Unlike simple parity bits that only detect errors, ECC enhances data integrity by correcting errors on the fly, which is critical for high-performance computing and mission-critical applications.

Key Differences Between Parity Bit and ECC

Parity bit provides basic error detection by adding a single bit to indicate whether the number of set bits is odd or even, enabling the identification of single-bit errors but not correcting them. ECC (Error Correcting Code) uses multiple bits and complex algorithms to detect and correct multiple-bit errors, ensuring higher data integrity and reliability in memory systems. While parity bits are simpler and require less overhead, ECC offers robust error correction capabilities critical for mission-critical and high-reliability hardware applications.

Use Cases: When to Use Parity Bit vs ECC

Parity bits are primarily used in simple hardware systems where detecting single-bit errors is sufficient, such as in basic memory modules or communication interfaces with low error rates. ECC is preferred for critical applications requiring both error detection and correction, including server memory, aerospace, and data storage systems where data integrity and fault tolerance are paramount. Employ parity bits for low-cost, minimal overhead error detection, while ECC is essential for environments needing robust error correction and reliability.

Performance Impact of Parity Bit and ECC

Parity Bit offers minimal performance overhead due to its simple single-bit error detection, making it suitable for high-speed data processing with low latency requirements. ECC provides robust error correction capabilities at the cost of increased computational complexity and memory usage, which can introduce additional latency and reduce throughput in hardware systems. Choosing between Parity Bit and ECC depends on the balance between acceptable error rates and performance demands in critical applications such as memory and communication interfaces.

Cost Analysis: Parity vs ECC in Hardware Systems

Parity bit implementation in hardware systems involves minimal additional circuitry, making it a cost-effective solution for error detection but limited to single-bit error identification. ECC requires more complex logic and additional memory overhead, which increases design and manufacturing costs but provides robust multi-bit error correction and enhanced system reliability. The choice between parity and ECC often hinges on the trade-off between acceptable error tolerance and budget constraints in mission-critical applications.

Reliability and Error Detection Capabilities

Parity bit provides basic error detection by identifying single-bit errors through simple odd or even parity checks, offering limited reliability in critical hardware systems. ECC (Error Correcting Code) enhances reliability by not only detecting but also correcting multi-bit errors, significantly reducing system failures in memory and data transmission. ECC's complex algorithms and additional redundancy bits enable robust error correction, making it essential for high-reliability applications like server memory and aerospace hardware.

Implementation Challenges in Modern Hardware

Parity bit implementation in modern hardware offers simplicity and low overhead but provides only single-bit error detection without correction capabilities. ECC (Error Correcting Code) requires more complex circuitry and increased silicon area to detect and correct multi-bit errors, posing challenges in power consumption and latency. Integrating ECC in high-density memories demands optimized algorithms and hardware architectures to balance reliability, performance, and resource constraints.

Future Trends in Error Detection and Correction Technologies

Emerging error detection and correction technologies are increasingly integrating advanced ECC algorithms capable of correcting multiple-bit errors, surpassing the capabilities of traditional parity bits that only detect single-bit errors. Machine learning techniques are being leveraged to optimize ECC code parameters for real-time adaptive error correction in hardware systems, enhancing reliability in high-speed memory and communication interfaces. Quantum computing hardware development further drives the evolution of error correction methods, necessitating robust codes that address quantum bit-flip and phase errors beyond classical parity and ECC schemes.

Parity Bit vs ECC (Error Correcting Code) Infographic

techiny.com

techiny.com