RISC (Reduced Instruction Set Computer) architecture streamlines hardware design by utilizing a limited set of simple instructions, which enhances performance through faster instruction execution and easier pipeline implementation. In contrast, CISC (Complex Instruction Set Computer) features a rich set of instructions that can execute multi-step operations within a single command, optimizing code density and memory usage. Hardware engineers often balance the trade-offs between RISC's efficiency and CISC's versatility when designing processors for specific applications.

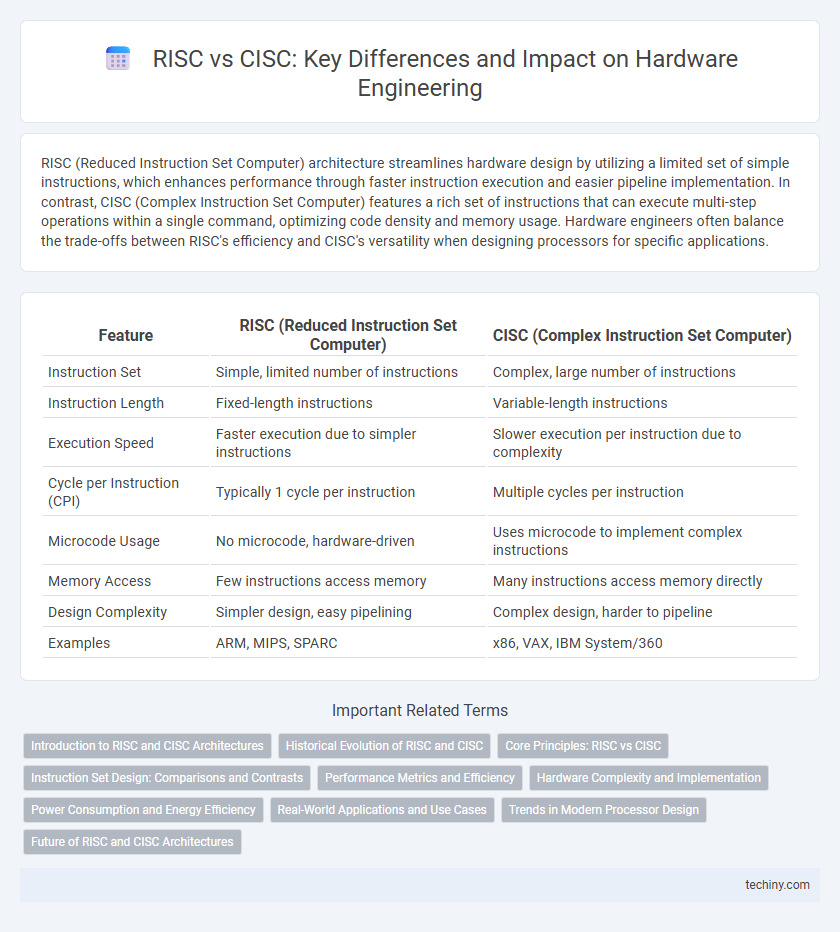

Table of Comparison

| Feature | RISC (Reduced Instruction Set Computer) | CISC (Complex Instruction Set Computer) |

|---|---|---|

| Instruction Set | Simple, limited number of instructions | Complex, large number of instructions |

| Instruction Length | Fixed-length instructions | Variable-length instructions |

| Execution Speed | Faster execution due to simpler instructions | Slower execution per instruction due to complexity |

| Cycle per Instruction (CPI) | Typically 1 cycle per instruction | Multiple cycles per instruction |

| Microcode Usage | No microcode, hardware-driven | Uses microcode to implement complex instructions |

| Memory Access | Few instructions access memory | Many instructions access memory directly |

| Design Complexity | Simpler design, easy pipelining | Complex design, harder to pipeline |

| Examples | ARM, MIPS, SPARC | x86, VAX, IBM System/360 |

Introduction to RISC and CISC Architectures

RISC (Reduced Instruction Set Computer) architecture emphasizes a simplified set of instructions to enable faster execution and greater efficiency in hardware design. CISC (Complex Instruction Set Computer) architecture incorporates a wide variety of instructions, allowing complex operations to be carried out with fewer lines of code. The core distinction lies in RISC's streamlined instruction pipeline versus CISC's rich instruction complexity, impacting processor performance and energy consumption.

Historical Evolution of RISC and CISC

The historical evolution of RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) reflects distinct design philosophies emerging in the 1970s to address processor efficiency and complexity. CISC architectures prioritized a rich instruction set to minimize program memory usage, exemplified by early Intel x86 processors, while RISC architectures, developed by institutions like UC Berkeley and Stanford, emphasized simplified instructions to achieve higher performance through pipelining and parallelism. The ongoing development led to hybrid approaches integrating RISC principles within traditionally CISC frameworks, optimizing instruction execution and power efficiency in modern CPUs.

Core Principles: RISC vs CISC

RISC architecture emphasizes a reduced set of simple instructions executed within a single clock cycle, optimizing pipeline efficiency and minimizing execution time. CISC architecture incorporates a complex set of instructions, enabling multi-step operations within single instructions, which can reduce code size but may increase clock cycles per instruction. Core principles of RISC focus on uniform instruction length and load/store operations, whereas CISC designs prioritize instruction complexity and memory-to-memory operations.

Instruction Set Design: Comparisons and Contrasts

RISC architecture features a simplified instruction set with fixed-length instructions that enable faster decoding and efficient pipelining, optimizing hardware performance. CISC incorporates a complex instruction set with variable-length instructions capable of executing multiple low-level operations per instruction, which reduces program size but complicates hardware design. The design trade-off impacts power consumption, instruction throughput, and compiler complexity, making RISC favorable for modern high-performance processors and CISC suitable for legacy and embedded systems.

Performance Metrics and Efficiency

RISC architectures deliver higher performance by utilizing simplified instructions that allow faster execution cycles and better pipeline efficiency, resulting in improved instruction throughput. CISC CPUs often execute more complex instructions per cycle, but their variable-length instruction sets can lead to increased decode time and power consumption, reducing overall efficiency. Performance metrics such as instructions per cycle (IPC), clock speed, and energy efficiency favor RISC designs in embedded systems due to streamlined processing and lower power requirements.

Hardware Complexity and Implementation

RISC (Reduced Instruction Set Computer) architectures feature simpler hardware design with a limited set of instructions, enabling faster instruction execution and easier pipelining. In contrast, CISC (Complex Instruction Set Computer) architectures have more hardware complexity due to their extensive instruction sets that often require multiple clock cycles for execution. This complexity in CISC leads to intricate control units and microcode implementations, increasing die size and power consumption compared to RISC processors.

Power Consumption and Energy Efficiency

RISC architectures generally consume less power and demonstrate higher energy efficiency due to their simplified instruction sets and reduced clock cycles per instruction. CISC designs, while capable of executing complex instructions, often require more transistors and longer execution times, leading to increased power consumption. Energy optimization in hardware engineering favors RISC implementations for mobile and embedded systems where power constraints are critical.

Real-World Applications and Use Cases

RISC (Reduced Instruction Set Computing) architectures excel in embedded systems, mobile devices, and real-time applications due to their simplified instruction sets that enable faster execution and lower power consumption, exemplified by ARM processors in smartphones and IoT devices. CISC (Complex Instruction Set Computing) architectures, typified by x86 processors in desktops and servers, handle complex software workloads efficiently by supporting a rich set of instructions that reduce program size and enhance compatibility with legacy applications. In high-performance computing and gaming, CISC's ability to execute complex instructions optimizes resource use, while RISC's efficiency benefits energy-sensitive environments like wearables and automotive control systems.

Trends in Modern Processor Design

Modern processor design increasingly favors RISC architectures due to their simplified instruction sets, enabling higher clock speeds and improved power efficiency critical for mobile and embedded systems. ARM processors exemplify this trend, dominating markets with scalable performance and low energy consumption. Although CISC designs like x86 maintain a strong presence in high-performance computing, the shift towards RISC reflects a broader industry emphasis on parallelism, reduced complexity, and better thermal management.

Future of RISC and CISC Architectures

RISC architectures emphasize simplicity and efficiency, enabling higher performance per watt and scalability in modern processors, making them a dominant choice for mobile and embedded systems. CISC designs continue to evolve through advanced microarchitectural techniques and micro-ops translation, maintaining relevance in desktop and server environments that require complex instruction handling. Industry trends suggest a hybrid approach, combining RISC's streamlined execution with CISC's rich instruction sets, will shape future hardware engineering innovations.

RISC vs CISC Infographic

techiny.com

techiny.com