Latches and flip-flops are fundamental memory elements used in hardware engineering for storing binary information, with latches being level-sensitive and flip-flops edge-triggered. Latches maintain their state as long as the enable signal is active, whereas flip-flops update their state only at specific clock edges, ensuring precise timing control. This difference makes flip-flops more suitable for synchronous circuits, while latches are often used in asynchronous designs or where simpler control is sufficient.

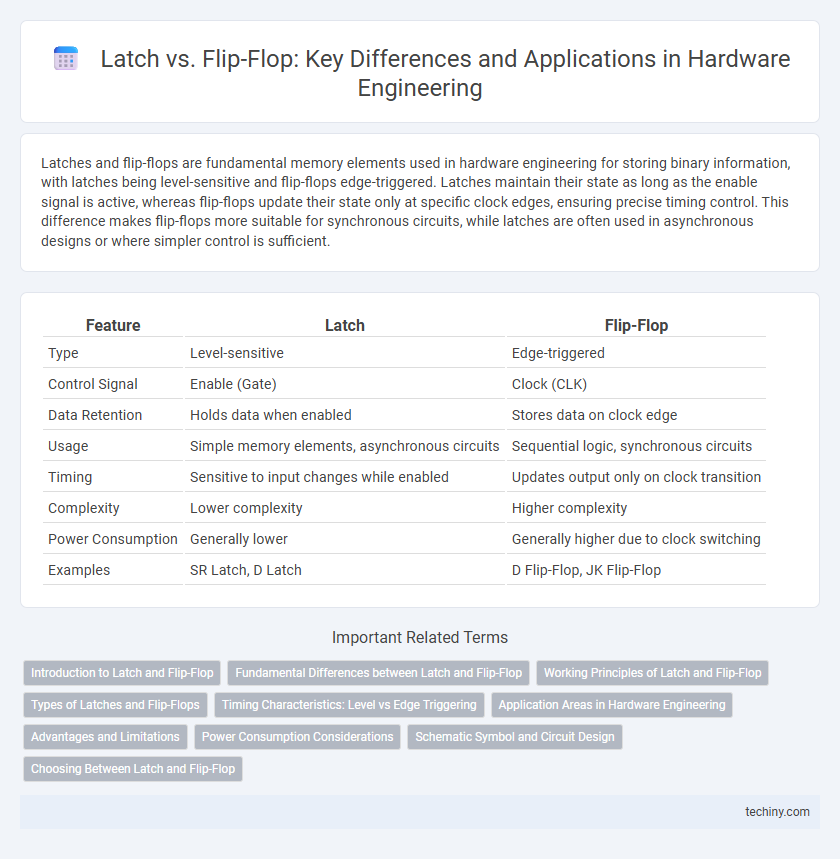

Table of Comparison

| Feature | Latch | Flip-Flop |

|---|---|---|

| Type | Level-sensitive | Edge-triggered |

| Control Signal | Enable (Gate) | Clock (CLK) |

| Data Retention | Holds data when enabled | Stores data on clock edge |

| Usage | Simple memory elements, asynchronous circuits | Sequential logic, synchronous circuits |

| Timing | Sensitive to input changes while enabled | Updates output only on clock transition |

| Complexity | Lower complexity | Higher complexity |

| Power Consumption | Generally lower | Generally higher due to clock switching |

| Examples | SR Latch, D Latch | D Flip-Flop, JK Flip-Flop |

Introduction to Latch and Flip-Flop

Latches and flip-flops are fundamental bistable devices used for storing binary information in hardware engineering. A latch is level-triggered and changes state when its enable signal is active, while a flip-flop is edge-triggered, capturing input on a clock signal's transition, which provides more precise timing control. Both components form the building blocks of sequential circuits, essential in digital memory and synchronization applications.

Fundamental Differences between Latch and Flip-Flop

Latches are level-sensitive devices that continuously monitor inputs and change output as long as the enable signal is active, whereas flip-flops are edge-triggered devices that update output only at specific clock edges, either rising or falling. Latches lack a clock input and are transparent when enabled, causing potential timing issues, while flip-flops provide synchronized data storage crucial for sequential logic circuits and precise timing control. The fundamental difference lies in timing control and data storage: latches respond to input changes during the enable level, whereas flip-flops capture and hold data strictly on clock transitions.

Working Principles of Latch and Flip-Flop

Latch operates as a level-sensitive bistable device that maintains its output state based on the input signal while the enable signal is active, continuously allowing data to pass through when enabled. Flip-flop functions as an edge-triggered bistable device that captures and stores input data only at specific clock transitions, ensuring data is sampled precisely on clock edges. The fundamental distinction in working principles lies in latch's transparency during the enable level versus flip-flop's exclusive latching on clock edge triggering for synchronous circuits.

Types of Latches and Flip-Flops

Latches include SR, D, and Gated Latches, each characterized by their level-sensitive operation and ability to hold data while the enable signal is active. Flip-flops, such as SR, D, JK, and T types, are edge-triggered devices designed to store data precisely at clock transitions, enhancing timing control in digital circuits. Selecting between these types depends on specific timing requirements and signal synchronization needs within hardware engineering projects.

Timing Characteristics: Level vs Edge Triggering

Latches are level-triggered devices that change output whenever the enable signal is active, making them highly sensitive to input variations during the enable phase. Flip-flops are edge-triggered, updating their output only at specific clock transitions, which enhances timing control and reduces glitches in synchronous circuits. This distinction makes flip-flops more suitable for precise timing applications, while latches offer simpler designs with faster response under certain conditions.

Application Areas in Hardware Engineering

Latches are widely used in asynchronous circuits and level-sensitive applications for temporary data storage due to their simpler design and faster response times. Flip-flops find extensive application in synchronous systems, including registers, counters, and memory devices, where edge-triggered operation ensures precise timing control and data stability. In hardware engineering, flip-flops dominate in clocked sequential logic, while latches serve effectively in low-power and speed-critical applications such as transparent data latching and glitch filtering.

Advantages and Limitations

Latches offer simpler design and lower power consumption, making them suitable for transparent data storage in asynchronous circuits, but they are vulnerable to glitches and race conditions due to their level-sensitive nature. Flip-flops provide edge-triggered operation, enabling synchronous data capture and improved stability, which is critical in clocked sequential circuits; however, their complexity and higher power usage can be a drawback in low-power applications. Choosing between latches and flip-flops depends on timing requirements, power constraints, and circuit design priorities within hardware engineering projects.

Power Consumption Considerations

Latch circuits typically consume less power than flip-flops due to their level-sensitive operation, which allows data to pass only when enabled, reducing unnecessary switching activity. Flip-flops, being edge-triggered, often exhibit higher power consumption because of frequent clocking and increased switching transitions at the clock edge. In low-power hardware design, selecting latches can optimize energy efficiency, especially in clock-gated or asynchronous domains.

Schematic Symbol and Circuit Design

Latch schematic symbols typically feature transparent gate inputs that control data flow, using simple circuit designs with fewer transistors to maintain state when enabled. Flip-flop symbols include a clock input and often edge-trigger indicators, reflecting more complex circuit designs with master-slave configurations for synchronized data storage. The design complexity of flip-flops provides improved timing control and avoids race conditions compared to latches.

Choosing Between Latch and Flip-Flop

Choosing between a latch and a flip-flop depends on the timing requirements and design complexity of the hardware system. Latches are level-sensitive devices ideal for asynchronous circuits or scenarios requiring transparency during specific clock levels, while flip-flops are edge-triggered, providing better control for synchronous designs and reducing timing hazards. Engineers must analyze setup and hold time constraints, as well as clock domain considerations, to select the most appropriate storage element for reliable and efficient data capture.

Latch vs Flip-flop Infographic

techiny.com

techiny.com