Synchronous buses operate based on a shared clock signal, ensuring data transfer occurs at precise, predictable intervals, which enhances timing coordination and simplifies circuit design. Asynchronous buses do not rely on a common clock, instead using handshaking signals to manage data transfers, allowing greater flexibility but requiring more complex control logic. The choice between synchronous and asynchronous bus architectures impacts system performance, complexity, and power consumption in hardware engineering designs.

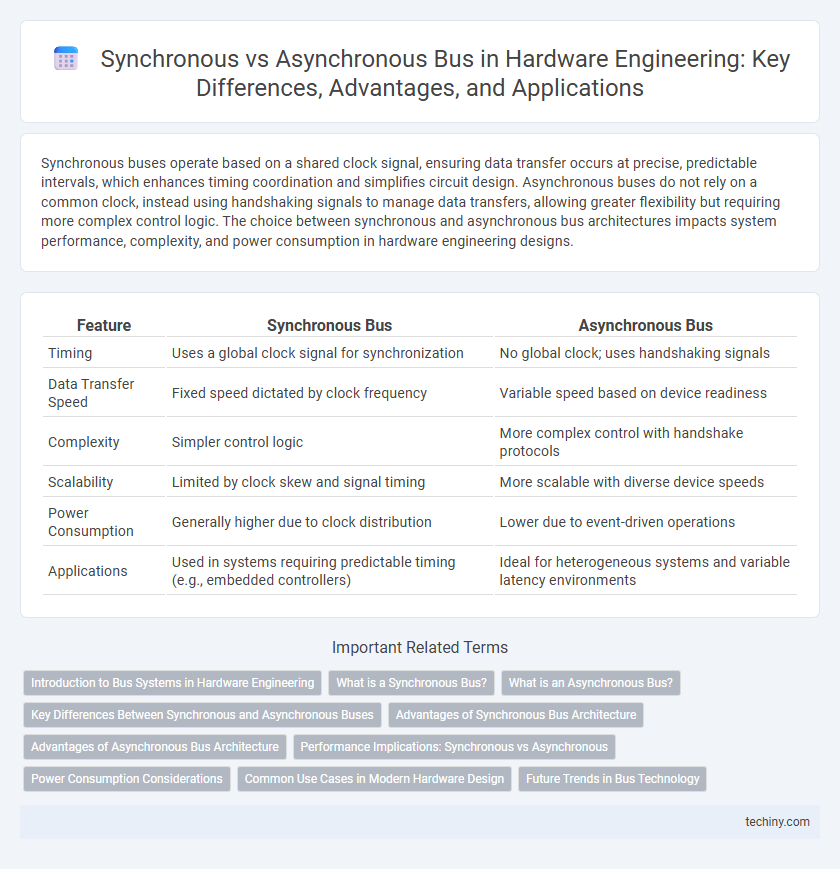

Table of Comparison

| Feature | Synchronous Bus | Asynchronous Bus |

|---|---|---|

| Timing | Uses a global clock signal for synchronization | No global clock; uses handshaking signals |

| Data Transfer Speed | Fixed speed dictated by clock frequency | Variable speed based on device readiness |

| Complexity | Simpler control logic | More complex control with handshake protocols |

| Scalability | Limited by clock skew and signal timing | More scalable with diverse device speeds |

| Power Consumption | Generally higher due to clock distribution | Lower due to event-driven operations |

| Applications | Used in systems requiring predictable timing (e.g., embedded controllers) | Ideal for heterogeneous systems and variable latency environments |

Introduction to Bus Systems in Hardware Engineering

Synchronous bus systems rely on a shared clock signal to coordinate data transfers, ensuring precise timing and reducing latency in hardware communication. Asynchronous bus systems operate without a global clock, using handshaking protocols to manage data synchronization, which provides flexibility in timing and compatibility with diverse device speeds. Understanding the differences between synchronous and asynchronous buses is critical for optimizing system performance and designing efficient hardware communication protocols.

What is a Synchronous Bus?

A synchronous bus is a communication system in hardware engineering where data transfer occurs in sync with a shared clock signal, ensuring all connected devices operate on the same timing reference. It enables predictable and coordinated data transmission, minimizing latency and timing errors during communication between components. This bus type is crucial in systems requiring precise timing control, such as microprocessors and memory modules.

What is an Asynchronous Bus?

An asynchronous bus operates without a shared clock signal, relying on handshake protocols to coordinate data transfer between devices. It allows components with different speeds to communicate efficiently by using request and acknowledge signals, ensuring data is transmitted only when both sender and receiver are ready. This flexibility reduces timing constraints and simplifies integration in complex hardware systems compared to synchronous buses.

Key Differences Between Synchronous and Asynchronous Buses

Synchronous buses operate based on a common clock signal, ensuring data transfer occurs at predictable intervals which simplifies timing and coordination between components. Asynchronous buses do not rely on a shared clock, using handshaking signals to manage data transfer, allowing greater flexibility but requiring more complex control logic. Key differences include timing method, complexity of control circuitry, and overall system synchronization.

Advantages of Synchronous Bus Architecture

Synchronous bus architecture offers precise timing control by operating with a shared clock signal, which ensures data transfers occur at predictable intervals, improving overall system reliability. This timing coordination reduces complexity in data synchronization and minimizes latency, leading to faster communication between hardware components. Enhanced system stability and simplified timing analysis are significant advantages that make synchronous buses ideal for high-speed, tightly-coupled hardware systems.

Advantages of Asynchronous Bus Architecture

Asynchronous bus architecture offers increased flexibility by allowing data transfer without a common clock signal, reducing timing constraints and improving system scalability. It enhances power efficiency by enabling components to operate at independent speeds, minimizing idle times and lowering energy consumption. This architecture also supports heterogeneous device integration, facilitating communication between modules with different clock domains and improving overall system reliability.

Performance Implications: Synchronous vs Asynchronous

Synchronous buses offer predictable latency and higher data throughput by relying on a global clock signal, which tightly coordinates data transfers and reduces timing uncertainties. In contrast, asynchronous buses trade off peak performance for flexibility, as they use handshaking protocols allowing components to operate at independent speeds but often incur additional wait states. System designs prioritizing maximum data rate and low latency typically favor synchronous buses, while asynchronous buses excel where device heterogeneity or power efficiency is critical.

Power Consumption Considerations

Synchronous buses consume more power due to continuous clock signal distribution, leading to higher dynamic power dissipation in hardware components. Asynchronous buses reduce power consumption by eliminating the global clock and enabling data transfer only when necessary, optimizing energy efficiency in hardware engineering. Selecting asynchronous bus architectures is crucial for low-power applications and extends battery life in embedded systems.

Common Use Cases in Modern Hardware Design

Synchronous buses dominate high-performance computing environments where precise timing and clock synchronization are critical, such as in CPUs and GPU data transfers. Asynchronous buses are favored in systems requiring flexibility across diverse clock domains, including embedded systems and inter-chip communications. Modern hardware design leverages synchronous buses for predictable data throughput, while asynchronous buses excel in low-power and mixed-speed modular architectures.

Future Trends in Bus Technology

Future trends in bus technology emphasize increased data transfer rates and power efficiency by integrating adaptive clocking mechanisms and intelligent handshaking protocols. Synchronous buses are evolving with dynamic frequency scaling and embedded phase-locked loops to minimize clock skew and support higher bandwidth demands. Asynchronous buses leverage event-driven timing and machine learning algorithms for latency reduction and improved fault tolerance in heterogeneous hardware environments.

Synchronous Bus vs Asynchronous Bus Infographic

techiny.com

techiny.com